Projects Showcase

Here are some of the important academic projects I participated in and contributed to

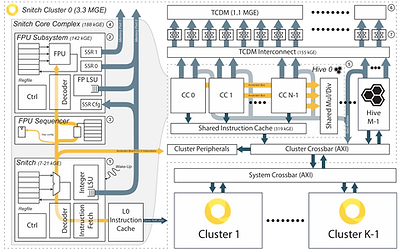

A RISC-V ISA Extension for Pseudo Dual-Issue Monte Carlo

October 2023 - April 2024

ETH Zurich, Zurich, Switzerland

-

Developed custom RISC-V ISA extensions and modified the microarchitecture of Snitch for optimized multithreaded execution

-

Implemented bare-metal Monte Carlo simulation programs supporting new extension using C and RISC-V assembly language

-

Analyzed bottlenecks and optimized performances, achieving a 1.8X IPC improvement, with 90% FPU utilization

-

Verified the custom extensions via RTL simulation and C-based testbench

-

Developed a topographical synthesis flow for PPA evaluations using gf12

Figure: F. Zaruba, F. Schuiki, T. Hoefler, and L. Benini, "Snitch: A tiny pseudo dual-issue processor for area and energy efficient execution of floating-point intensive workloads," ACM Transactions on Architecture and Code Optimization, vol. 17, no. 1, pp. 1-25, 2020. doi: 10.1145/3386326.

Towards Open-Source: ASICs: Physical Implementation Gap-Analysis of a Linux-Capable SoC Vehicle in 130nm CMOS

February 2023 - June 2022

ETH Zurich, Zurich, Switzerland

-

Implemented baseline physical backend designs for IHP130 technology as a baseline of a linux-capable SoC Iguana

-

Added step-by-step openness into the physical designs using Open source PDK provided by IHP, and open-synthesized netlist by yosys

-

Participated two standard cell hackathons which made changes to the cells using Cadence Virtuoso

-

Evaluated and compared different physical implementations statistically

-

The final chip was named Iguana and contributed to preparation of a final .gds file to the foundry on June 29th, 2023

Figure: Floor planning of Iguana

Reference Links:

https://github.com/pulp-platform/cheshire

Figure: final .gds sent to foundry

Investigation of the T-head Floating Point Division and Square Root Unit

February 2022 - May 2022

ETH Zurich, Zurich, Switzerland

-

Integrated T-head’s floating point arithmetic module (32-bit) into the current FPU of ETH’s Pulpissimo microcontroller architecture

-

Analyzed and compared the algorithms, latencies, performances, areas, and powers used in T-head’s FPU and Pulpissimo’s FPU

-

Conducted a full chip design flow: a synthesis of the FPU and a back-end flow which includes floorplanning, place & route using TSMC 65nm technology.

-

Conducted a technical presentation under the supervision of Prof. Luca Benini's Integrated Systems Laboratory (IIS)

-

Prepared a professional report in Latex.

Figure: T-HEAD Xuantie E906

Photo adapted from https://www.t-head.cn

Figure: FPU Top Level with subgroups

Photo adapted from presentation, May 30th, 2021

Reference Links:

https://github.com/T-head-Semi/openc906

https://github.com/pulp-platform?q=cv&type=all&language=&sort=

Implementation and Overhead Analysis of an OpenMP Kernel Based on Its Bare-metal Counterpart on Snitch

July 2023 - August 2023

ETH Zurich, Zurich, Switzerland

-

Port a bare-metal kernel application (already available on Snitch) to OpenMP using its compiler directives and runtime library

-

Comparison runtime of OpenMP and bare-metal AXPY

-

Investigate causes of overhead introduced by OpenMP

Reference Links:

https://github.com/pulp-platform/snitch_cluster

Independent Chip Testing: Kairos

July 2023

ETH Zurich, Zurich, Switzerland

-

Collaborated with teammate to configure the basic setup for testing Kairos, a TSMC65 chip implementing a power controller for HPC systems, using automatic test equipment (ATE) available at IIS lab.

-

Carried out the first successful continuity test, a functional test using test vectors generated using VCD method, as well as a JTAG minimal boost test.

-

Profiled reference clock frequency and also collected static power measurements for the core and pads, dynamic power measurements for the core of the chip, namely Kairos.

Figure: Testflow Setup on ATE

Reference Links:

http://asic.ethz.ch/2022/Kairos.html

Bachelor’s Thesis-Intuitive Thrombectomy Control

September 2020 - March 2021

Worcester, MA, USA

-

Conducted literature review regarding thrombectomy and available medical devices in targeting blood clots removal

-

Evaluated the risks that surgeons face when doing a thrombectomy surgery.

-

Collaboratively designed linear force feedback and torque force feedback mechanisms that allow a brain surgeon to perform remote surgery with standard guidewire manipulation techniques

-

Installed controllers via coding with Arduino Mega 2560, which reads and processes the data of the haptic feedback mechanisms for post data processing

-

Turned the controller via Arduino IDE

-

Produced a professional report and delivered a final project presentation

Figure: Control Box of the Haptic Feedback System

Reference: Lu, Y., Litovchick, S., Batista, R., & Jiang, L. (2021). An Intuitive User Interface for Teleoperated Robotic Neuro-Intervention. : Worcester Polytechnic Institute.

NASA University Student Launch Initiative (USLI)

September 2018 - April 2019

Worcester, MA, USA

-

Integrated Radio transceivers Adafruit RFM95W Lora

-

Collaboratively designed PCB layout using Fritzing

-

Conducted tests on the performances of transceivers

-

Delivered PDR and CDR to NASA; rocket launched in Marshall Space Flight Center in Huntsville, Alabama